# **OpenACC Programming** and Best Practices Guide

May 2021

# **OpenACC**

More Science, Less Programming

# Contents

| 1 | Intr | roduction 1                                 |

|---|------|---------------------------------------------|

|   | 1.1  | Writing Portable Code                       |

|   |      | 1.1.1 Libraries                             |

|   |      | 1.1.2 Standard Programming Languages        |

|   |      | 1.1.3 Compiler Directives                   |

|   |      | 1.1.4 Parallel Programming Extensions       |

|   | 1.2  | What is OpenACC?                            |

|   |      | 1.2.1 The OpenACC Accelerator Model         |

|   |      | 1.2.2 Benefits and Limitations of OpenACC   |

|   | 1.3  | Accelerating an Application with OpenACC    |

|   |      | 1.3.1 OpenACC Directive Syntax              |

|   |      | 1.3.2 Porting Cycle                         |

|   |      | 1.3.3 Heterogenous Computing Best Practices |

|   | 1.4  | Case Study - Jacobi Iteration               |

| 2 | Ass  | ess Application Performance 10              |

|   | 2.1  | Baseline Profiling                          |

|   | 2.2  | Additional Profiling                        |

|   | 2.3  | Case Study - Analysis                       |

| 3 | Par  | allelize Loops 15                           |

| U | 3.1  | The Kernels Construct                       |

|   | 3.2  | The Parallel Construct   16                 |

|   | 3.3  | Differences Between Parallel and Kernels    |

|   | 3.4  | The Loop Construct       19                 |

|   | 0.1  | 3.4.1 private                               |

|   |      | 3.4.2 reduction                             |

|   | 3.5  | Routine Directive                           |

|   | 0.0  | 3.5.1 C++ Class Functions                   |

|   | 3.6  | Atomic Operations                           |

|   | 0.0  | 3.6.1 Atomic Example                        |

|   | 3.7  | Case Study - Parallelize                    |

|   |      | 3.7.1 Parallel Loop                         |

|   |      | 3.7.2 Kernels                               |

| <b>4</b> | Opt                                           | timize Data Locality                                                                                                                                                                                                                                               | 29                                                                                |  |  |  |  |  |  |  |  |

|----------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|          | 4.1                                           | Data Regions                                                                                                                                                                                                                                                       | 29                                                                                |  |  |  |  |  |  |  |  |

|          | 4.2                                           | Data Clauses                                                                                                                                                                                                                                                       | 30                                                                                |  |  |  |  |  |  |  |  |

|          |                                               | 4.2.1 Shaping Arrays                                                                                                                                                                                                                                               | 31                                                                                |  |  |  |  |  |  |  |  |

|          | 4.3                                           | Unstructured Data Lifetimes                                                                                                                                                                                                                                        | 32                                                                                |  |  |  |  |  |  |  |  |

|          |                                               | 4.3.1 C++ Class Data $\ldots$                                                                                                                                                                                                                                      | 33                                                                                |  |  |  |  |  |  |  |  |

|          | 4.4                                           | Update Directive                                                                                                                                                                                                                                                   | 35                                                                                |  |  |  |  |  |  |  |  |

|          | 4.5                                           | Best Practice: Offload Inefficient Operations to Maintain Data Locality                                                                                                                                                                                            | 36                                                                                |  |  |  |  |  |  |  |  |

|          | 4.6                                           | Case Study - Optimize Data Locality                                                                                                                                                                                                                                | 37                                                                                |  |  |  |  |  |  |  |  |

| <b>5</b> | Opt                                           | timize Loops                                                                                                                                                                                                                                                       | 41                                                                                |  |  |  |  |  |  |  |  |

|          | 5.1                                           | Efficient Loop Ordering                                                                                                                                                                                                                                            | 41                                                                                |  |  |  |  |  |  |  |  |

|          | 5.2                                           | OpenACC's 3 Levels of Parallelism                                                                                                                                                                                                                                  | 41                                                                                |  |  |  |  |  |  |  |  |

|          |                                               | 5.2.1 Understanding OpenACC's Three Levels of Parallelism                                                                                                                                                                                                          | 43                                                                                |  |  |  |  |  |  |  |  |

|          | 5.3                                           | Mapping Parallelism to the Hardware                                                                                                                                                                                                                                | 44                                                                                |  |  |  |  |  |  |  |  |

|          | 5.4                                           | Collapse Clause                                                                                                                                                                                                                                                    | 46                                                                                |  |  |  |  |  |  |  |  |

|          | 5.5                                           | Routine Parallelism                                                                                                                                                                                                                                                |                                                                                   |  |  |  |  |  |  |  |  |

|          | 5.6                                           | Case Study - Optimize Loops                                                                                                                                                                                                                                        | 47                                                                                |  |  |  |  |  |  |  |  |

|          |                                               |                                                                                                                                                                                                                                                                    |                                                                                   |  |  |  |  |  |  |  |  |

| 6        | Ope                                           | enACC Interoperability                                                                                                                                                                                                                                             | 53                                                                                |  |  |  |  |  |  |  |  |

| 6        | <b>Ор</b> е<br>6.1                            | enACC Interoperability The Host Data Region                                                                                                                                                                                                                        | <b>53</b><br>53                                                                   |  |  |  |  |  |  |  |  |

| 6        | -                                             | The Host Data Region                                                                                                                                                                                                                                               |                                                                                   |  |  |  |  |  |  |  |  |

| 6        | 6.1                                           | The Host Data Region                                                                                                                                                                                                                                               | 53                                                                                |  |  |  |  |  |  |  |  |

| 6        | 6.1<br>6.2                                    | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54                                                                          |  |  |  |  |  |  |  |  |

| 6        | $6.1 \\ 6.2 \\ 6.3$                           | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56                                                                    |  |  |  |  |  |  |  |  |

| 6        | $6.1 \\ 6.2 \\ 6.3$                           | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56                                                              |  |  |  |  |  |  |  |  |

| 6        | $6.1 \\ 6.2 \\ 6.3$                           | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56                                                        |  |  |  |  |  |  |  |  |

| 6        | 6.1<br>6.2<br>6.3<br>6.4                      | The Host Data RegionUsing Device PointersObtaining Device and Host Pointer AddressesAdditional Vendor-Specific Interoperability Features6.4.1Asynchronous Queues and CUDA Streams (NVIDIA)6.4.2CUDA Managed Memory (NVIDIA)6.4.3Using CUDA Device Kernels (NVIDIA) | 53<br>54<br>56<br>56<br>56<br>56                                                  |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4                      | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b>                               |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4                      | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58                         |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4                      | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58<br>61                   |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4<br><b>Adv</b><br>7.1 | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58<br>61<br>66             |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4<br><b>Adv</b><br>7.1 | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58<br>61                   |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4<br><b>Adv</b><br>7.1 | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58<br>61<br>66<br>66       |  |  |  |  |  |  |  |  |

|          | 6.1<br>6.2<br>6.3<br>6.4<br><b>Adv</b><br>7.1 | The Host Data Region                                                                                                                                                                                                                                               | 53<br>54<br>56<br>56<br>56<br>56<br>57<br><b>58</b><br>58<br>61<br>66<br>66<br>67 |  |  |  |  |  |  |  |  |

#### A References

# Chapter 1

# Introduction

This guide presents methods and best practices for accelerating applications in an incremental, performance portable way. Although some of the examples may show results using a given compiler or accelerator, the information presented in this document is intended to address all architectures both available at publication time and well into the future. Readers should be comfortable with C, C++, or Fortran, but do not need experience with parallel programming or accelerated computing, although such experience will be helpful.

Note: This guide is a community effort. To contribute, please visit the project on Github.

# 1.1 Writing Portable Code

The current computing landscape is spotted with a variety of computing architectures: multi-core CPUs, GPUs, many-core devices, DSPs, ARM processors, and FPGAs, to name a few. It is now commonplace to find not just one, but several of these differing architectures within the same machine. Programmers must make portability of their code a forethought, otherwise they risk locking their application to a single architecture, which may limit the ability to run on future architectures. Although the variety of architectures may seem daunting to the programmer, closer analysis reveals trends that show a lot in common between them. The first thing to note is that all of these architectures are moving in the direction of more parallelism. CPUs are not only adding CPU cores but also expanding the length of their SIMD operations. GPUs have grown to require a high degree of block and SIMT parallelism. It is clear that going forward all architectures will require a significant degree of parallelism in order to achieve high performance. Modern processors need not only a large amount of parallelism, but frequently expose multiple levels of parallelism with varying degrees of coarseness. The next thing to notice is that all of these architectures have exposed hierarchies of memory. CPUs have the main system memory, typically DDR, and multiple layers of cache memory. GPUs have the main CPU memory, the main GPU memory, and various degrees of cache or scratchpad memory. Additionally on hybrid architectures, which include two or more different architectures, there exist machines where the two architectures have completely separate memories, some with physically separate but logically the same memory, and some with fully shared memory.

Because of these complexities, it's important that developers choose a programming model that balances the need for portability with the need for performance. Below are four programming models of varying degrees of both portability and performance. In a real application it's frequently best to use a mixture of approaches to ensure a good balance between high portability and performance.

## 1.1.1 Libraries

Standard (and *de facto* standard) libraries provide the highest degree of portability because the programmer can frequently replace only the library used without even changing the source code itself when changing compute architectures. Since many hardware vendors provide highly-tuned versions of common libraries, using libraries can also result in very high performance. Although libraries can provide both high portability and high performance, few applications are able to use only libraries because of their limited scope.

Some vendors provide additional libraries as a value-add for their platform, but which implement non-standard APIs. These libraries provide high performance, but little portability. Fortunately because libraries provide modular APIs, the impact of using non-portable libraries can be isolated to limit the impact on overall application portability.

#### 1.1.2 Standard Programming Languages

Many standard programming languages either have or are beginning to adopt features for parallel programming. For example, Fortran 2008 added support for do concurrent, which exposes the potential parallelism with that loop, and C++17 added support for std::execution, which enables users to express parallelism with certain loop structures. Adoption of these language features is often slow, however, and many standard languages are only now beginning to discuss parallel programming features for future language releases. When these features become commonplace, they will provide high portability, since they are part of a standard language, and if well-designed can provide high performance as well.

#### 1.1.3 Compiler Directives

When standard programming languages lack support for necessary features compiler directives can provide additional functionality. Directives, in the form of pragmas in C/C++ and comments in Fortran, provide additional information to compilers on how to build and/or optimize the code. Most compilers support their own directives, and also directives such as OpenACC and OpenMP, which are backed by industry groups and implemented by a range of compilers. When using industrybacked compiler directives the programmer can write code with a high degree of portability across compilers and architectures. Frequently, however, these compiler directives are written to remain very high level, both for simplicity and portability, meaning that performance may lag lower-level programming paradigms. Many developers are willing to give up 10-20% of hand-tuned performance in order to get a high degree of portability to other architectures and to enhance programmer productivity. The tolerance for this portability/performance trade-off will vary according to the needs of the programmer and application.

#### 1.1.4 Parallel Programming Extensions

CUDA and OpenCL are examples of extensions to existing programming languages to give additional parallel programming capabilities. Code written in these languages is frequently at a lower level than that of other options, but as a result can frequently achieve higher performance. Lower level architectural details are exposed and the way that a problem is decomposed to the hardware must be explicitly managed with these languages. This is the best option when performance goals outweigh portability, as the low-level nature of these programming languages frequently makes the resulting code less portable. Good software engineering practices can reduce the impact these languages have on portability.

There is no one programming model that fits all needs. An application developer needs to evaluate the priorities of the project and make decisions accordingly. A best practice is to begin with the most portable and productive programming models and move to lower level programming models only as needed and in a modular fashion. In doing so the programmer can accelerate much of the application very quickly, which is often more beneficial than attempting to get the absolute highest performance out of a particular routine before moving to the next. When development time is limited, focusing on accelerating as much of the application as possible is generally more productive than focusing solely on the top time consuming routine.

# 1.2 What is OpenACC?

With the emergence of GPU and many-core architectures in high performance computing, programmers desire the ability to program using a familiar, high level programming model that provides both high performance and portability to a wide range of computing architectures. OpenACC emerged in 2011 as a programming model that uses high-level compiler directives to expose parallelism in the code and parallelizing compilers to build the code for a variety of parallel accelerators. This document is intended as a best practices guide for accelerating an application using OpenACC to give both good performance and portability to other devices.

### 1.2.1 The OpenACC Accelerator Model

In order to ensure that OpenACC would be portable to all computing architectures available at the time of its inception and into the future, OpenACC defines an abstract model for accelerated computing. This model exposes multiple levels of parallelism that may appear on a processor as well as a hierarchy of memories with varying degrees of speed and addressability. The goal of this model is to ensure that OpenACC will be applicable to more than just a particular architecture or even just the architectures in wide availability at the time, but to ensure that OpenACC could be used on future devices as well.

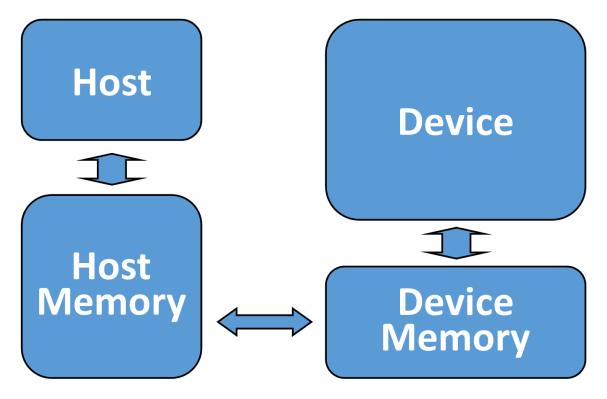

At its core OpenACC supports offloading of both computation and data from a *host* device to an *accelerator* device. In fact, these devices may be the same or may be completely different architectures, such as the case of a CPU host and GPU accelerator. The two devices may also have separate memory spaces or a single memory space. In the case that the two devices have different memories the OpenACC compiler and runtime will analyze the code and handle any accelerator memory management and the transfer of data between host and device memory. Figure 1.1 shows a high level diagram of the OpenACC abstract accelerator, but remember that the devices and memories may be physically the same on some architectures.

Figure 1.1: OpenACC's Abstract Accelerator Model

More details of OpenACC's abstract accelerator model will be presented throughout this guide when they are pertinent.

**Best Practice:** For developers coming to OpenACC from other accelerator programming models, such as CUDA or OpenCL, where host and accelerator memory is frequently represented by two distinct variables (host\_A[] and device\_A[], for instance), it's important to remember that when using OpenACC a variable should be thought of as a single object, regardless of whether it's backed by memory in one or more memory spaces. If one assumes that a variable represents two separate memories, depending on where it is used in the program, then it is possible to write programs that access the variable in unsafe ways, resulting in code that would not be portable to devices that share a single memory between the host and device. As with any parallel or asynchronous programming paradigm, accessing the same variable from two sections of code simultaneously could result in a race condition that produces inconsistent results. By assuming that you are always accessing a single variable, regardless of how it is stored in memory, the programmer will avoid making mistakes that could cost a significant amount of effort to debug.

#### **1.2.2** Benefits and Limitations of OpenACC

OpenACC is designed to be a high-level, platform independent language for programming accelerators. As such, one can develop a single source code that can be run on a range of devices and achieve good performance. The simplicity and portability that OpenACC's programming model provides sometimes comes at a cost to performance. The OpenACC abstract accelerator model defines a least common denominator for accelerator devices, but cannot represent architectural specifics of these devices without making the language less portable. There will always be some optimizations that are possible in a lower-level programming model, such as CUDA or OpenCL, that cannot be represented at a high level. For instance, although OpenACC has the **cache** directive, some uses of *shared memory* on NVIDIA GPUs are more easily represented using CUDA. The same is true for any host or device: certain optimizations are too low-level for a high-level approach like OpenACC. It is up to the developers to determine the cost and benefit of selectively using a lower level programming language for performance critical sections of code. In cases where performance is too critical to take a high-level approach, it's still possible to use OpenACC for much of the application, while using another approach in certain places, as will be discussed in a later chapter on interoperability.

# 1.3 Accelerating an Application with OpenACC

This section will detail an incremental approach to accelerating an application using OpenACC. When taking this approach it is beneficial to revisit each step multiple times, checking the results of each step for correctness. Working incrementally will limit the scope of each change for improved productivity and debugging.

#### 1.3.1 OpenACC Directive Syntax

This guide will introduce OpenACC directives incrementally, as they become useful for the porting process. All OpenACC directives have a common syntax, however, with the acc sentinal, designating to the compiler that the text that follows will be OpenACC, a directive, and clauses to that directive, many of which are optional but provide the compiler with additional information.

In C and C++, these directives take the form of a pragma. The example code below shows the OpenACC kernels directive without any additional clauses

#pragma acc kernels

In Fortran, the directives take the form of a special comment, as demonstrated below.

1 !\$acc kernels

Some OpenACC directives apply to structured blocks of code, while others are executable statements. In C and C++ a block of code can be represented by curly braces ({ and }). In Fortran a block of code will begin with an OpenACC directive (!**\$acc kernels**) and end with a matching ending directive (!**\$acc end kernels**).

## 1.3.2 Porting Cycle

Programmers should take an incremental approach to accelerating applications using OpenACC to ensure correctness. This guide will follow the approach of first assessing application performance, then using OpenACC to parallelize important loops in the code, next optimizing data locality to remove unnecessary data migrations between the host and accelerator, and finally optimizing loops within the code to maximize performance on a given architecture. This approach has been successful in many applications because it prioritizes changes that are likely to provide the greatest returns so that the programmer can quickly and productively achieve the acceleration.

There are two important things to note before detailing each step. First, at times during this process application performance may actually slow down. Developers should not become frustrated if their initial efforts result in a loss of performance. As will be explained later, this is generally the result of implicit data movement between the host and accelerator, which will be optimized as a part of the porting cycle. Second, it is critical that developers check the program results for correctness after each change. Frequent correctness checks will save a lot of debugging effort, since errors can be found and fixed immediately, before they have the chance to compound. Some developers may find it beneficial to use a source version control tool to snapshot the code after each successful change so that any breaking changes can be quickly thrown away and the code returned to a known good state.

#### 1.3.2.1 Assess Application Performance

Before one can begin to accelerate an application it is important to understand in which routines and loops an application is spending the bulk of its time and why. It is critical to understand the most time-consuming parts of the application to maximize the benefit of acceleration. Amdahl's Law informs us that the speed-up achievable from running an application on a parallel accelerator will be limited by the remaining serial code. In other words, the application will see the most benefit by accelerating as much of the code as possible and by prioritizing the most time-consuming parts. A variety of tools may be used to identify important parts of the code, including simple application timers.

#### 1.3.2.2 Parallelize Loops

Once important regions of the code have been identified, OpenACC directives should be used to accelerate these regions on the target device. Parallel loops within the code should be decorated with OpenACC directives to provide OpenACC compilers the information necessary to parallelize the code for the target architecture.

#### 1.3.2.3 Optimize Data Locality

Because many accelerated architectures, such as CPU + GPU architectures, use distinct memory spaces for the *host* and *device* it is necessary for the compiler to manage data in both memories and move the data between the two memories to ensure correct results. Compilers rarely have full knowledge of the application, so they must be cautious in order to ensure correctness, which often involves copying data to and from the accelerator more often than is actually necessary. The programmer can give the compiler additional information about how to manage the memory so that it remains local to the accelerator as long as possible and is only moved between the two memories when absolutely necessary. Programmers will often realize the largest performance gains after optimizing data movement during this step.

#### 1.3.2.4 Optimize Loops

Compilers will make decisions about how to map the parallelism in the code to the target accelerator based on internal heuristics and the limited knowledge it has about the application. Sometimes additional performance can be gained by providing the compiler with more information so that it can make better decisions on how to map the parallelism to the accelerator. When coming from a traditional CPU architecture to a more parallel architecture, such as a GPU, it may also be necessary to restructure loops to expose additional parallelism for the accelerator or to reduce the frequency of data movement. Frequently code refactoring that was motivated by improving performance on parallel accelerators is beneficial to traditional CPUs as well.

This process is by no means the only way to accelerate using OpenACC, but it has been proven successful in numerous applications. Doing the same steps in different orders may cause both frustration and difficulty debugging, so it's advisable to perform each step of the process in the order shown above.

#### **1.3.3** Heterogenous Computing Best Practices

Many applications have been written with little or even no parallelism exposed in the code. The applications that do expose parallelism frequently do so in a coarse-grained manner, where a small number of threads or processes execute for a long time and compute a significant amount work each. Modern GPUs and many-core processors, however, are designed to execute fine-grained threads, which are short-lived and execute a minimal amount of work each. These parallel architectures achieve high throughput by trading single-threaded performance in favor of several orders in magnitude more parallelism. This means that when accelerating an application with OpenACC, which was designed in light of increased hardware parallelism, it may be necessary to refactor the code to favor tightly-nested loops with a significant amount of data reuse. In many cases these same code changes also benefit more traditional CPU architectures as well by improving cache use and vectorization.

OpenACC may be used to accelerate applications on devices that have a discrete memory or that have a memory space that's shared with the host. Even on devices that utilize a shared memory there is frequently still a hierarchy of a fast, close memory for the accelerator and a larger, slower memory used by the host. For this reason it is important to structure the application code to maximize reuse of arrays regardless of whether the underlying architecture uses discrete or unified memories. When refactoring the code for use with OpenACC it is frequently beneficial to assume a discrete memory, even if the device you are developing on has a unified memory. This forces data locality to be a primary consideration in the refactoring and will ensure that the resulting code exploits hierarchical memories and is portable to a wide range of devices.

56

57

58

#### Case Study - Jacobi Iteration 1.4

Throughout this guide we will use simple applications to demonstrate each step of the acceleration process. The first such application will solve the 2D-Laplace equation with the iterative Jacobi solver. Iterative methods are a common technique to approximate the solution of elliptic PDEs, like the 2D-Laplace equation, within some allowable tolerance. In the case of our example we will perform a simple stencil calculation where each point calculates it value as the mean of its neighbors values. The calculation will continue to iterate until either the maximum change in value between two iterations drops below some tolerance level or a maximum number of iterations is reached. For the sake of consistent comparison through the document the examples will always iterate 1000 times. The main iteration loop for both C/C++ and Fortran appears below.

```

while ( error > tol && iter < iter_max )</pre>

52

{

53

error = 0.0;

54

55

for( int j = 1; j < n-1; j++)</pre>

56

{

57

for( int i = 1; i < m-1; i++ )</pre>

58

{

59

Anew[j][i] = 0.25 * (A[j][i+1] + A[j][i-1])

60

+ A[j-1][i] + A[j+1][i]);

61

error = fmax( error, fabs(Anew[j][i] - A[j][i]));

62

}

63

}

64

65

for( int j = 1; j < n-1; j++)</pre>

66

{

67

for( int i = 1; i < m-1; i++ )</pre>

68

{

69

A[j][i] = Anew[j][i];

70

}

71

}

72

73

if(iter % 100 == 0) printf("%5d, %0.6f\n", iter, error);

74

75

iter++;

76

}

77

do while ( error .gt. tol .and. iter .lt. iter_max )

52

error=0.0 fp kind

53

54

do j=1,m-2

55

do i=1,n-2

```

Anew(i,j) =  $0.25_{fp_kind} * (A(i+1,j) + A(i-1,j) + \&$

A(i, j-1) + A(i, j+1))

```

error = max( error, abs(Anew(i,j)-A(i,j)) )

59

end do

60

end do

61

62

do j=1,m-2

63

do i=1,n-2

64

A(i,j) = Anew(i,j)

65

end do

66

end do

67

68

if(mod(iter,100).eq.0) write(*,'(i5,f10.6)'), iter, error

69

iter = iter + 1

70

71

```

```

end do

```

72

The outermost loop in each example will be referred to as the *convergence loop*, since it loops until the answer has converged by reaching some maximum error tolerance or number of iterations. Notice that whether or not a loop iteration occurs depends on the error value of the previous iteration. Also, the values for each element of **A** is calculated based on the values of the previous iteration, known as a data dependency. These two facts mean that this loop cannot be run in parallel.

The first loop nest within the convergence loop calculates the new value for each element based on the current values of its neighbors. Notice that it is necessary to store this new value into a different array. If each iteration stored the new value back into itself then a data dependency would exist between the data elements, as the order each element is calculated would affect the final answer. By storing into a temporary array we ensure that all values are calculated using the current state of **A** before **A** is updated. As a result, each loop iteration is completely independent of each other iteration. These loop iterations may safely be run in any order or in parallel and the final result would be the same. This loop also calculates a maximum error value. The error value is the difference between the new value and the old. If the maximum amount of change between two iterations is within some tolerance, the problem is considered converged and the outer loop will exit.

The second loop nest simply updates the value of A with the values calculated into Anew. If this is the last iteration of the convergence loop, A will be the final, converged value. If the problem has not yet converged, then A will serve as the input for the next iteration. As with the above loop nest, each iteration of this loop nest is independent of each other and is safe to parallelize.

In the coming sections we will accelerate this simple application using the method described in this document.

# Chapter 2

# **Assess Application Performance**

A variety of tools can be used to evaluate application performance and which are available will depend on your development environment. From simple application timers to graphical performance analyzers, the choice of performance analysis tool is outside of the scope of this document. The purpose of this section is to provide guidance on choosing important sections of code for acceleration, which is independent of the profiling tools available.

Throughout this guide, the NVIDIA Nsight Systems performance analysis tool which is provided with the CUDA toolkit, will be used for CPU profiling. When accelerator profiling is needed, the application will be run on an NVIDIA GPU and the NVIDIA Nsight Systems profiler will be again be used.

# 2.1 Baseline Profiling

Before parallelizing an application with OpenACC the programmer must first understand where time is currently being spent in the code. Routines and loops that take up a significant percentage of the runtime are frequently referred to as *hot spots* and will be the starting point for accelerating the application. A variety of tools exist for generating application profiles, such as gprof, Vampir, Nsight Systems, and TAU. Selecting the specific tool that works best for a given application is outside of the scope of this document, but regardless of which tool or tools are used below are some important pieces of information that will help guide the next steps in parallelizing the application.

- Application performance How much time does the application take to run? How efficiently does the program use the computing resources?

- Program hotspots In which routines is the program spending most of its time? What is being done within these important routines? Focusing on the most time consuming parts of the application will yield the greatest results.

- Performance limiters Within the identified hotspots, what's currently limiting the application performance? Some common limiters may be I/O, memory bandwidth, cache reuse, floating point performance, communication, etc. One way to evaluate the performance limiters of a given loop nest is to evaluate its *computational intensity*, which is a measure of how many

operations are performed on a data element per load or store from memory.

• Available parallelism - Examine the loops within the hotspots to understand how much work each loop nest performs. Do the loops iterate 10's, 100's, 1000's of times (or more)? Do the loop iterations operate independently of each other? Look not only at the individual loops, but look a nest of loops to understand the bigger picture of the entire nest.

Gathering baseline data like the above both helps inform the developer where to focus efforts for the best results and provides a basis for comparing performance throughout the rest of the process. It's important to choose input that will realistically reflect how the application will be used once it has been accelerated. It's tempting to use a known benchmark problem for profiling, but frequently these benchmark problems use a reduced problem size or reduced I/O, which may lead to incorrect assumptions about program performance. Many developers also use the baseline profile to gather the expected output of the application to use for verifying the correctness of the application as it is accelerated.

# 2.2 Additional Profiling

Through the process of porting and optimizing an application with OpenACC it's necessary to gather additional profile data to guide the next steps in the process. Some profiling tools, such as Nsight Systems and Vampir, support profiling on CPUs and GPUs, while other tools, such as gprof, may only support profiling on a particular platform. Additionally, some compilers build their own profiling into the application, such is the case with the NVHPC compiler, which supports setting the NVCOMPILER\_ACC\_TIME environment variable for gathering runtime information about the application. When developing on offloading platforms, such as CPU + GPU platforms, it's generally important to use a profiling tool throughout the development process that can evaluate both time spent in computation and time spent performing PCIe data transfers. This document will use NVIDIA Nsight Systems Profiler for performing this analysis, although it is only available on NVIDIA platforms.

# 2.3 Case Study - Analysis

To get a better understanding of the case study program we will use the NVIDIA NSight Systems command line interface that comes as a part of the CUDA Toolkit and NVIDIA HPC SDK. First, it's necessary to build the executable. Remember to use the flags included in the example below to ensure that additional information about how the compiler optimized the program is displayed. The executable is built with the following command:

```

$ nvc -fast -Minfo=all laplace2d.c

GetTimer:

21, include "timer.h"

61, FMA (fused multiply-add) instruction(s) generated

main:

41, Loop not fused: function call before adjacent loop

Loop unrolled 8 times

49, StartTimer inlined, size=2 (inline) file laplace2d.c (37)

52, FMA (fused multiply-add) instruction(s) generated

```

- 58, Generated vector simd code for the loop containing reductions

- 68, Memory copy idiom, loop replaced by call to \_\_c\_mcopy8

- 79, GetTimer inlined, size=10 (inline) file laplace2d.c (54)

Once the executable has been built, the **nsys** command will run the executable and generate a profiling report that can be viewed offline in the NVIDIA Nsight Systems GUI

```

$ nsys profile ./a.out

```

```

Jacobi relaxation Calculation: 4096 x 4096 mesh

0, 0.250000

100, 0.002397

200, 0.001204

300, 0.000804

400, 0.000603

500, 0.000483

600, 0.000403

700, 0.000345

800, 0.000302

900, 0.000269

total: 36.480533 s

Processing events...

Capturing symbol files...

Saving temporary "/tmp/nsys-report-2f5b-f32e-7dec-9af0.qdstrm" file to disk...

Creating final output files...

```

Report file moved to "/home/ubuntu/openacc-programming-guide/examples/laplace/ch2/report1.qdrep"

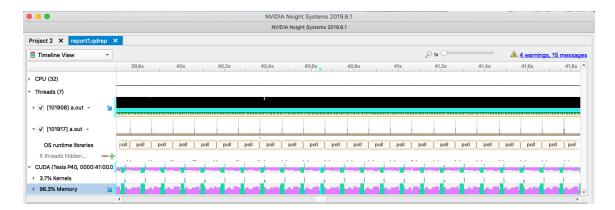

Once the data has been collected, and the .qdrep report has been generated, it can be visualized using the Nsight Systems GUI. You must first copy the report (report1.qdrep in the example above) to a machine that has graphical capabilities and download the Nsight Systems interface. Next, you must open the application and select your file via the file manager.

When we open the report in Nsight Systems, we see that the vast majority of the time is spent in two routines: main and <u>c</u>\_mcopy8. A screenshot of the initial screen for Nsight systems is shown in figure 2.1. Since the code for this case study is completely within the main function of the program, it's not surprising that nearly all of the time is spent in main, but in larger applications it's likely that the time will be spent in several other routines.

Clicking into the main function we can see that nearly all of the runtime within main comes from the loop that calculates the next value for A. This is shown in figure 2.2. What is not obvious from the profiler output, however, is that the time spent in the memory copy routine shown in the initial screen is actually the second loop nest, which performs the array swap at the end of each iteration. The compiler output shows above that the loop at line 68 was replaced by a memory copy, because doing so is more efficient than copying each element individually. So what the profiler is really showing us is that the major hotspots for our application are the loop nest that calculate Anew from A and the loop nest that copies from Anew to A for the next iteration, so we'll concentrate our

| •                            | New Dreiset     | 90 1 | NVIDIA Nsight Systems 2019.6.1 |

|------------------------------|-----------------|------|--------------------------------|

| <b>•</b>                     | New Project     | ЖN   |                                |

|                              | Open            | жΟ   | NVIDIA Nsight Systems 2019.6.1 |

| ante de M                    | Import          | жI   |                                |

| roject 2 🗙                   | Close Project 2 | жw   |                                |

| Select target for profiling. | Close Floject 2 |      |                                |

| eeleet talget iel proming.   |                 |      |                                |

| Select a target to see avail | able options.   |      | Start                          |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      |                                |

|                              |                 |      | <u>@</u>                       |

Figure 2.1: Nsight Systems initial window in the GUI. You must use the toolbar at the top to find your target report file

| •••                                                                                                                                              |    | NVIDIA | A Nsight Systems 201   | 9.6.1 |         |                         |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|------------------------|-------|---------|-------------------------|--|--|--|--|

|                                                                                                                                                  |    | NVID   | IA Nsight Systems 2019 | 6.1   |         |                         |  |  |  |  |

| Project 2 X report1.qdrep X                                                                                                                      |    |        |                        |       |         |                         |  |  |  |  |

| Timeline View                                                                                                                                    |    |        |                        |       | D 1x    | A warnings, 10 messages |  |  |  |  |

|                                                                                                                                                  | 5s | 10s    | 15s                    | 20s   | 25s 30s | 35s 🔺                   |  |  |  |  |

| ▶ CPU (32)                                                                                                                                       | _  |        |                        |       |         |                         |  |  |  |  |

| <ul> <li>Threads (3)</li> </ul>                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

| ▶ 🗸 [107793] a.out 👻                                                                                                                             |    |        |                        |       |         |                         |  |  |  |  |

| 3 threads hidden 🗕 🕂                                                                                                                             | -  |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  | 4  |        |                        |       |         | •                       |  |  |  |  |

| Bottom-Up View  Process [107793] a.out (3 of 3 threads)                                                                                          |    |        |                        |       |         |                         |  |  |  |  |

| Tilter 71,871 samples are used.                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

|                                                                                                                                                  |    |        |                        |       |         |                         |  |  |  |  |

| main 81.59 /usa/thuber/openacc-best-practices-guide/examples/laplace/ch2/a.out<br>c_mcopy8_avx 17.81 /opt/pg/linux86-64-Ilvm/19.10/lib/libpgc.so |    |        |                        |       |         |                         |  |  |  |  |

Figure 2.2: Nsight initial profile window showing 81% of runtime in main and 17% in a memory copy routine.

efforts on these two loop nests.

In the chapters that follow, we will optimize the loops identified in this chapter as the hotspots within our example application.

# Chapter 3

# Parallelize Loops

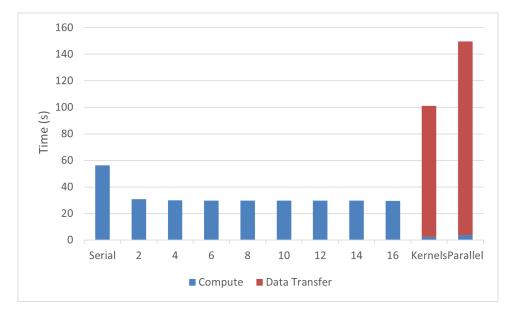

Now that the important hotspots in the application have been identified, the programmer should incrementally accelerate these hotspots by adding OpenACC directives to the important loops within those routines. There is no reason to think about the movement of data at this point in the process, the OpenACC compiler will analyze the data needed in the identified region and automatically ensure that the data is available on the accelerator. By focusing solely on the parallelism during this step, the programmer can move as much computation to the device as possible and ensure that the program is still giving correct results before optimizing away data motion in the next step. During this step in the process it is common for the overall runtime of the application to increase, even if the execution of the individual loops is faster using the accelerator. This is because the compiler must take a cautious approach to data movement, frequently copying more data to and from the accelerator than is actually necessary. Even if overall execution time increases during this step, the developer should focus on expressing a significant amount of parallelism in the code before moving on to the next step and realizing a benefit from the directives.

OpenACC provides two different approaches for exposing parallelism in the code: **parallel** and **kernels** regions. Each of these directives will be detailed in the sections that follow.

# 3.1 The Kernels Construct

The kernels construct identifies a region of code that may contain parallelism, but relies on the automatic parallelization capabilities of the compiler to analyze the region, identify which loops are safe to parallelize, and then accelerate those loops. Developers with little or no parallel programming experience, or those working on functions containing many loop nests that might be parallelized, will find the kernels directive a good starting place for OpenACC acceleration. The code below demonstrates the use of kernels in both C/C++ and Fortran.

1 #pragma acc kernels

2 {

3 for (i=0; i<N; i++)</pre>

```

{

4

y[i] = 0.0f;

\mathbf{5}

x[i] = (float)(i+1);

6

}

7

8

for (i=0; i<N; i++)</pre>

9

{

10

y[i] = 2.0f * x[i] + y[i];

11

}

12

}

13

```

```

!$acc kernels

1

do i=1,N

^{2}

y(i) = 0

3

x(i) = i

4

enddo

\mathbf{5}

6

do i=1,N

7

y(i) = 2.0 * x(i) + y(i)

8

enddo

9

!$acc end kernels

10

```

In this example the code is initializing two arrays and then performing a simple calculation on them. Notice that we have identified a block of code, using curly braces in C and starting and ending directives in Fortran, that contains two candidate loops for acceleration. The compiler will analyze these loops for data independence and parallelize both loops by generating an accelerator *kernel* for each. The compiler is given complete freedom to determine how best to map the parallelism available in these loops to the hardware, meaning that we will be able to use this same code regardless of the accelerator we are building for. The compiler will use its own knowledge of the target accelerator to choose the best path for acceleration. One caution about the kernels directive, however, is that if the compiler cannot be certain that a loop is data independent, it will not parallelize the loop. Common reasons for why a compiler may misidentify a loop as non-parallel will be discussed in a later section.

## 3.2 The Parallel Construct

The parallel construct identifies a region of code that will be parallelized across OpenACC gangs. By itself a parallel region is of limited use, but when paired with the loop directive (discussed in more detail later) the compiler will generate a parallel version of the loop for the accelerator. These two directives can, and most often are, combined into a single parallel loop directive. By placing this directive on a loop the programmer asserts that the affected loop is safe to parallelize and allows the compiler to select how to schedule the loop iterations on the target accelerator. The code below demonstrates the use of the parallel loop combined directive in both C/C++ and Fortran.

```

1

#pragma acc parallel loop

for (i=0; i<N; i++)</pre>

2

3

{

y[i] = 0.0f;

4

x[i] = (float)(i+1);

\mathbf{5}

}

6

#pragma acc parallel loop

8

for (i=0; i<N; i++)</pre>

9

{

10

y[i] = 2.0f * x[i] + y[i];

11

}

12

```

```

!$acc parallel loop

1

do i=1,N

2

y(i) = 0

3

x(i) = i

4

enddo

5

6

!$acc parallel loop

7

do i=1,N

8

y(i) = 2.0 * x(i) + y(i)

9

10

enddo

```

Notice that, unlike the kernels directive, each loop needs to be explicitly decorated with parallel loop directives. This is because the parallel construct relies on the programmer to identify the parallelism in the code rather than performing its own compiler analysis of the loops. In this case, the programmer is only identifying the availability of parallelism, but still leaving the decision of how to map that parallelism to the accelerator to the compiler's knowledge about the device. This is a key feature that differentiates OpenACC from other similar programming models. The programmer identifies the parallelism without dictating to the compiler how to exploit that parallelism. This means that OpenACC code will be portable to devices other than the device on which the code is being developed, because details about how to parallelize the code are left to compiler knowledge rather than being hard-coded into the source.

# 3.3 Differences Between Parallel and Kernels

One of the biggest points of confusion for new OpenACC programmers is why the specification has both the **parallel** and **kernels** directives, which appear to do the same thing. While they are very closely related there are subtle differences between them. The **kernels** construct gives the compiler maximum leeway to parallelize and optimize the code how it sees fit for the target accelerator, but also relies most heavily on the compiler's ability to automatically parallelize the code. As a result, the programmer may see differences in what different compilers are able to parallelize and how they do so. The **parallel loop** directive is an assertion by the programmer that it is both safe and desirable to parallelize the affected loop. This relies on the programmer to have correctly identified parallelism in the code and remove anything in the code that may be unsafe to parallelize. If the programmer asserts incorrectly that the loop may be parallelized then the resulting application may produce incorrect results.

To put things another way: the **kernels** construct may be thought of as a hint to the compiler of where it should look for parallelism while the **parallel** directive is an assertion to the compiler of where there is parallelism.

An important thing to note about the kernels construct is that the compiler will analyze the code and only parallelize when it is certain that it is safe to do so. In some cases the compiler may not have enough information at compile time to determine whether a loop is safe to parallelize, in which case it will not parallelize the loop, even if the programmer can clearly see that the loop is safely parallel. For example, in the case of C/C++ code, where arrays are represented as pointers, the compiler may not always be able to determine that two arrays do not reference the same memory, otherwise known as *pointer aliasing*. If the compiler cannot know that two pointers are not aliased it will not be able to parallelize a loop that accesses those arrays.

**Best Practice:** C programmers should use the restrict keyword (or the \_\_restrict decorator in C++) whenever possible to inform the compiler that the pointers are not aliased, which will frequently give the compiler enough information to then parallelize loops that it would not have otherwise. In addition to the restrict keyword, declaring constant variables using the const keyword may allow the compiler to use a read-only memory for that variable if such a memory exists on the accelerator. Use of const and restrict is a good programming practice in general, as it gives the compiler additional information that can be used when optimizing the code.

Fortran programmers should also note that an OpenACC compiler will parallelize Fortran array syntax that is contained in a kernels construct. When using parallel instead, it will be necessary to explicitly introduce loops over the elements of the arrays.

One more notable benefit that the kernels construct provides is that if data is moved to the device for use in loops contained in the region, that data will remain on the device for the full extent of the region, or until it is needed again on the host within that region. This means that if multiple loops access the same data it will only be copied to the accelerator once. When parallel loop is used on two subsequent loops that access the same data a compiler may or may not copy the data back and forth between the host and the device between the two loops. In the examples shown in the previous section the compiler generates implicit data movement for both parallel loops, but only generates data movement once for the kernels approach, which may result in less data motion by default. This difference will be revisited in the case study later in this chapter.

For more information on the differences between the kernels and parallel directives, please see [http://www.pgroup.com/lit/articles/insider/v4n2a1.htm].

At this point many programmers will be left wondering which directive they should use in their code. More experienced parallel programmers, who may have already identified parallel loops within their code, will likely find the **parallel loop** approach more desirable. Programmers with less parallel programming experience or whose code contains a large number of loops that need to be analyzed may find the **kernels** approach much simpler, as it puts more of the burden on the compiler. Both approaches have advantages, so new OpenACC programmers should determine for themselves which

approach is a better fit for them. A programmer may even choose to use kernels in one part of the code, but parallel in another if it makes sense to do so.

**Note:** For the remainder of the document the phrase *parallel region* will be used to describe either a **parallel** or **kernels** region. When refering to the **parallel** construct, a terminal font will be used, as shown in this sentence.

# **3.4** The Loop Construct

The loop construct gives the compiler additional information about the very next loop in the source code. The loop directive was shown above in connection with the **parallel** directive, although it is also valid with kernels. Loop clauses come in two forms: clauses for correctness and clauses for optimization. This chapter will only discuss the two correctness clauses and a later chapter will discuss optimization clauses.

#### 3.4.1 private

The private clause specifies that each loop iteration requires its own copy of the listed variables. For example, if each loop contains a small, temporary array named tmp that it uses during its calculation, then this variable must be made private to each loop iteration in order to ensure correct results. If tmp is not declared private, then threads executing different loop iterations may access this shared tmp variable in unpredictable ways, resulting in a race condition and potentially incorrect results. Below is the synax for the private clause.

private(var1, var2, var3, ...)

There are a few special cases that must be understood about scalar variables within loops. First, loop iterators will be privatized by default, so they do not need to be listed as private. Second, unless otherwise specified, any scalar accessed within a parallel loop will be made *first private* by default, meaning a private copy will be made of the variable for each loop iteration and it will be initialized with the value of that scalar upon entering the region. Finally, any variables (scalar or not) that are declared within a loop in C or C++ will be made private to the iterations of that loop by default.

Note: The **parallel** construct also has a **private** clause which will privatize the listed variables for each gang in the parallel region.

#### 3.4.2 reduction

The reduction clause works similarly to the private clause in that a private copy of the affected variable is generated for each loop iteration, but reduction goes a step further to reduce all of those private copies into one final result, which is returned from the region. For example, the maximum of all private copies of the variable may be required. A reduction may only be specified on a scalar variable and only common, specified operations can be performed, such as +, \*, min, max, and various bitwise operations (see the OpenACC specification for a complete list). The format of the reduction clause is as follows, where *operator* should be replaced with the operation of interest and *variable* should be replaced with the variable being reduced:

#### reduction(operator:variable)

An example of using the reduction clause will come in the case study below.

## 3.5 Routine Directive

Function or subroutine calls within parallel loops can be problematic for compilers, since it's not always possible for the compiler to see all of the loops at one time. OpenACC 1.0 compilers were forced to either inline all routines called within parallel regions or not parallelize loops containing routine calls at all. OpenACC 2.0 introduced the **routine** directive to address this shortcoming. The **routine** directive gives the compiler the necessary information about the function or subroutine and the loops it contains in order to parallelize the calling parallel region. The routine directive must be added to a function definition informing the compiler of the level of parallelism used within the routine. OpenACC's *levels of parallelism* will be discussed in a later section.

## 3.5.1 C++ Class Functions

When operating on C++ classes, it's frequently necessary to call class functions from within parallel regions. The example below shows a C++ class float3 that contains 3 floating point values and has a set function that is used to set the values of its x, y, and z members to that of another instance of float3. In order for this to work from within a parallel region, the set function is declared as an OpenACC routine using the routine directive. Since we know that it will be called by each iteration of a parallel loop, it's declared a seq (or sequential) routine.

```

class float3 {

1

public:

2

float x,y,z;

3

4

#pragma acc routine seq

5

void set(const float3 *f) {

6

x=f->x;

7

y=f->y;

z=f->z;

9

}

10

};

11

```

## **3.6** Atomic Operations

When one or more loop iterations need to access an element in memory at the same time data races can occur. For instance, if one loop iteration is modifying the value contained in a variable and another is trying to read from the same variable in parallel, different results may occur depending on which iteration occurs first. In serial programs, the sequential loops ensure that the variable will be modified and read in a predictable order, but parallel programs don't make guarantees that a particular loop iteration will happen before another. In simple cases, such as finding a sum, maximum, or minimum value, a reduction operation will ensure correctness. For more complex operations, the **atomic** directive will ensure that no two threads can attempt to perfom the contained operation simultaneously. Use of atomics is sometimes a necessary part of parallelization to ensure correctness.

The **atomic** directive accepts one of four clauses to declare the type of operation contained within the region. The **read** operation ensures that no two loop iterations will read from the region at the same time. The **write** operation will ensure that no two iterations with write to the region at the same time. An **update** operation is a combined read and write. Finally a **capture** operation performs an update, but saves the value calculated in that region to use in the code that follows. If no clause is given, then an update operation will occur.

#### 3.6.1 Atomic Example

A histogram is a common technique for counting up how many times values occur from an input set according to their value. The example code below loops through a series of integer numbers of a known range and counts the occurances of each number in that range. Since each number in the range can occur multiple times, we need to ensure that each element in the histogram array is updated atomically. The code below demonstrates using the **atomic** directive to generate a histogram.

```

#pragma acc parallel loop

1

for(int i=0;i<HN;i++)</pre>

2

h[i]=0;

3

4

#pragma acc parallel loop

5

for(int i=0;i<N;i++) {</pre>

6

#pragma acc atomic update

7

h[a[i]]+=1;

8

}

9

!$acc kernels

1

h(:) = 0

2

!$acc end kernels

3

!$acc parallel loop

4

```

```

5 do i=1,N

6 !$acc atomic

7 h(a(i)) = h(a(i)) + 1

8 enddo

9 !$acc end parallel loop

```

Notice that updates to the histogram array **h** are performed atomically. Because we are incrementing the value of the array element, an update operation is used to read the value, modify it, and then write it back.

# 3.7 Case Study - Parallelize

In the last chapter we identified the two loop nests within the convergence loop as the most time consuming parts of our application. Additionally we looked at the loops and were able to determine that the outer convergence loop is not parallel, but the two loops nested within are safe to parallelize. In this chapter we will accelerate those loop nests with OpenACC using the directives discussed earlier in this chapter. To further emphasize the similarities and differences between parallel and kernels directives, we will accelerate the loops using both and discuss the differences.

#### 3.7.1 Parallel Loop

We previously identified the available parallelism in our code, now we will use the **parallel loop** directive to accelerate the loops that we identified. Since we know that the two doubly-nested sets of loops are parallel, simply add a **parallel loop** directive above each of them. This will inform the compiler that the outer of the two loops is safely parallel. Some compilers will additionally analyze the inner loop and determine that it is also parallel, but to be certain we will also add a **loop** directive around the inner loops.

There is one more subtlety to accelerating the loops in this example: we are attempting to calculate the maximum value for the variable **error**. As discussed above, this is considered a *reduction* since we are reducing from all possible values for **error** down to just the single maximum. This means that it is necessary to indicate a reduction on the first loop nest (the one that calculates **error**).

**Best Practice:** Some compilers will detect the reduction on **error** and implicitly insert the **reduction** clause, but for maximum portability the programmer should always indicate reductions in the code.

At this point the code looks like the examples below.

```

while ( error > tol && iter < iter_max )</pre>

52

{

53

error = 0.0;

54

55

#pragma acc parallel loop reduction(max:error)

56

for( int j = 1; j < n-1; j++)</pre>

57

{

58

#pragma acc loop reduction(max:error)

59

for( int i = 1; i < m-1; i++ )</pre>

60

{

61

A[j][i] = 0.25 * (Anew[j][i+1] + Anew[j][i-1])

62

+ Anew[j-1][i] + Anew[j+1][i]);

63

error = fmax( error, fabs(A[j][i] - Anew[j][i]));

64

}

65

}

66

67

#pragma acc parallel loop

68

for( int j = 1; j < n-1; j++)</pre>

69

{

70

```

```

71

#pragma acc loop

for( int i = 1; i < m-1; i++ )</pre>

72

{

73

A[j][i] = Anew[j][i];

74

}

75

}

76

77

if(iter % 100 == 0) printf("%5d, %0.6f\n", iter, error);

78

79

iter++;

80

}

81

```

```

do while ( error .gt. tol .and. iter .lt. iter_max )

52

error=0.0_fp_kind

53

54

!$acc parallel loop reduction(max:error)

55

do j=1,m-2

56

!$acc loop reduction(max:error)

57

do i=1,n-2

58

A(i,j) = 0.25_fp_kind * ( Anew(i+1,j ) + Anew(i-1,j ) + &

59

Anew(i ,j-1) + Anew(i ,j+1))

60

error = max( error, abs(A(i,j) - Anew(i,j)) )

61

end do

62

end do

63

64

!$acc parallel loop

65

do j=1,m-2

66

!$acc loop

67

do i=1,n-2

68

A(i,j) = Anew(i,j)

69

end do

70

end do

71

72

73

if(mod(iter,100).eq.0) write(*,'(i5,f10.6)'), iter, error

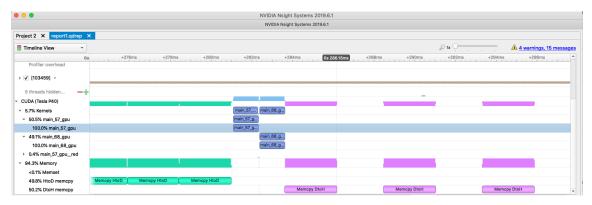

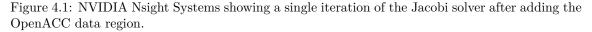

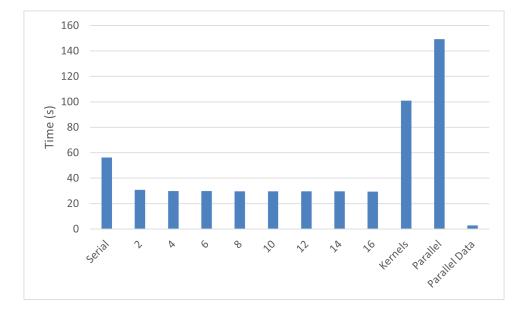

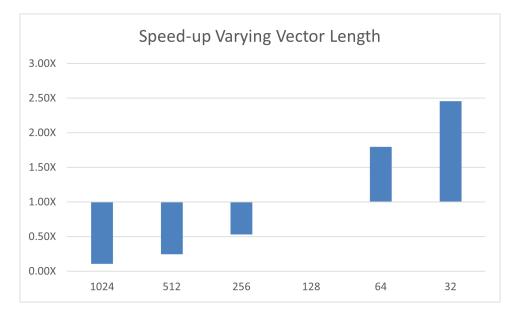

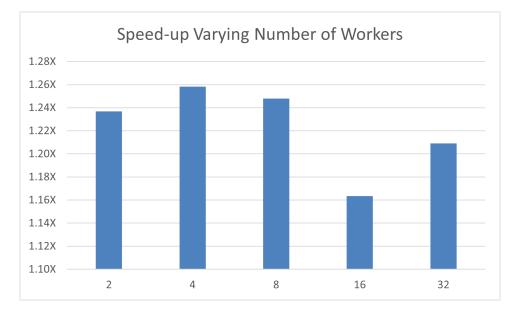

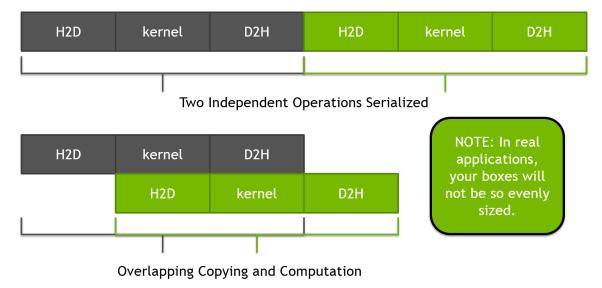

iter = iter + 1